Tin công nghệ

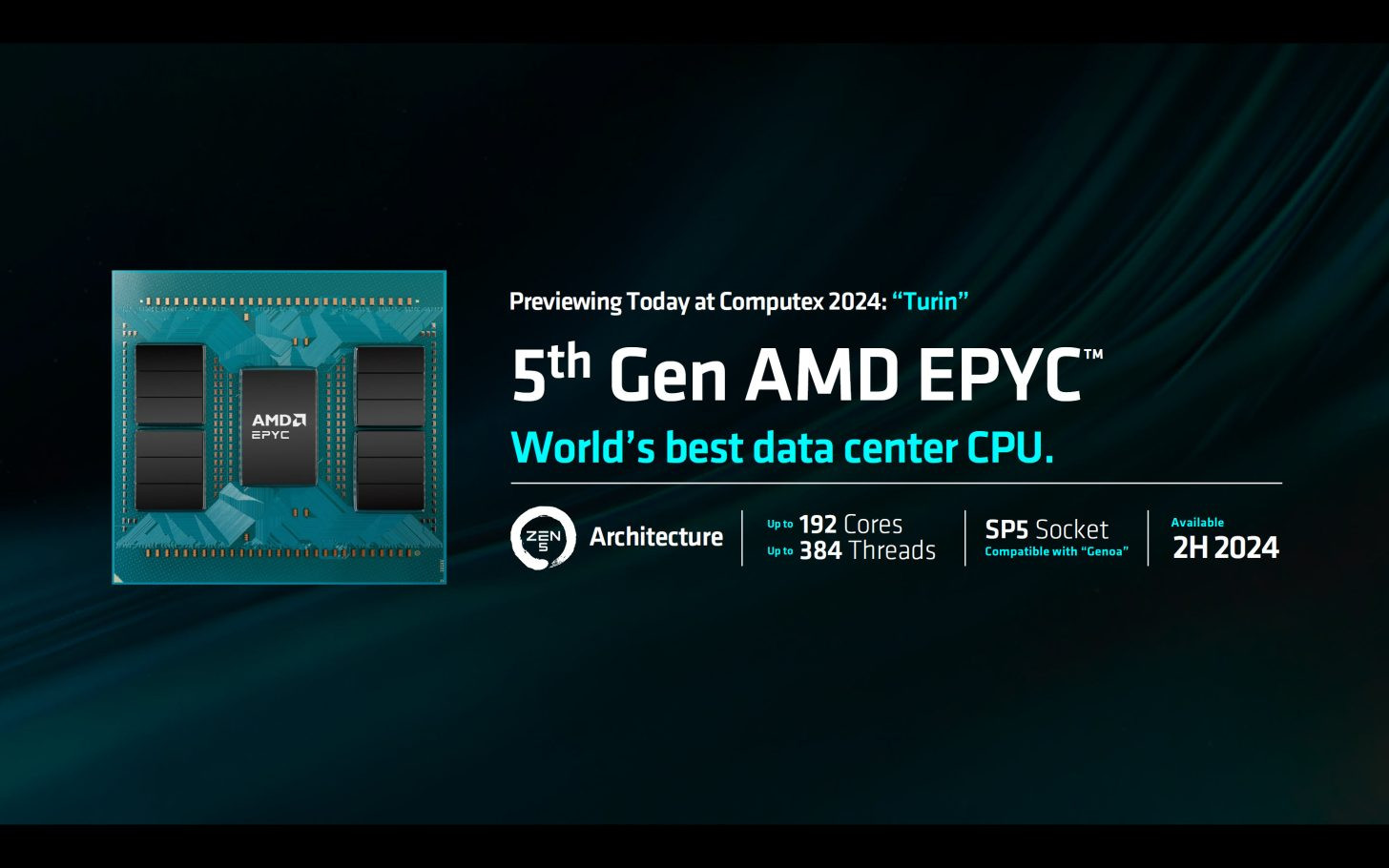

AMD ra mắt CPU Thế hệ 5 EPYC "Turin": Lên đến 192 nhân "Zen 5", 384 luồng trên ổ SP5 & Sẽ có mặt vào nửa cuối năm 2024.

AMD đã chính thức giới thiệu dòng CPU thế hệ tiếp theo EPYC 9005 "Turin" của mình, mang đến tới 192 lõi Zen 5 vào nửa sau của năm 2024.

AMD cuối cùng đã mở màn cho "siêu phẩm" Trung Tâm Dữ Liệu thế hệ tiếp theo của mình, CPU EPYC Turin dựa trên Zen 5, dự kiến sẽ được gắn nhãn dưới dòng sản phẩm EPYC 9005 và tính năng một loạt các chip đa dạng từ tính toán, đám mây, điện thoại, biên dạng được tối ưu hóa. AMD không cung cấp cho chúng ta bất kỳ thông số cụ thể nào vào thời điểm này nhưng điều họ đang nói với chúng ta là Intel nên cảm thấy rất sợ hãi về điều sắp xảy ra vì Turin trông như một con quái vật!

Cho đến nay, chúng ta đã thấy các SKUs như EPYC 9845 (160 Nhân / 320 Luồng), 9825 (144 Nhân / 288 Luồng), 9745 (128 Nhân / 256 Luồng), 9655 (96 Nhân / 192 Luồng), 9645 (96 Nhân / 192 Luồng), và 9565 (72 Nhân / 144 Luồng). Tất cả các SKUs này đều là các biến thể 64 Nhân trở lên và có hơn 256 MB bộ nhớ cache L3 và TDP dao động từ 320/400 đến 500W. Dưới đây là các cấu hình CPU khác nhau mà chúng ta nên mong đợi trong gia đình EPYC Turin:

100-000000976-09 - 12 CCD + 1 IOD (192 Nhân Zen 5C / 384 Luồng / 384 MB Cache / 500W)

100-000001152-05 - 10 CCD + 1 IOD (160 Nhân Zen 5C / 320 Luồng / 320 MB Cache / 360W)

100-000001153-09 - 8 CCD + 1 IOD (128 Nhân Zen 5C / 256 Luồng / 256 MB Cache)

100-000001249 -XX - 2 CCD + 1 IOD (32 Nhân Zen 5C / 64 Luồng / 64 MB Cache)

100-000001538-03 - 16 CCD + 1 IOD (128 Nhân Zen 5 / 256 Luồng / 512 MB Cache)

100-000001245-XX - 16 CCD + 1 IOD (128 Nhân Zen 5 / 256 Luồng / 512 MB Cache)

100-000001246-02 - 12 CCD + 1 IOD (96 Nhân Zen 5 / 192 Luồng / 384 MB Cache)

100-000001341-XX - 12 CCD + 1 IOD (96 Nhân Zen 5 / 192 Luồng / 384 MB Cache)

100-000001247-12 - 8 CCD + 1 IOD (64 Nhân Zen 5 / 128 Luồng / 256 MB Cache)

100-000001247-04 - 8 CCD + 1 IOD (64 Nhân Zen 5 / 128 Luồng / TBD MB Cache)

100-000001342-XX - 8 CCD + 1 IOD (64 Nhân Zen 5 / 128 Luồng / 256 MB Cache)

100-000001538-03 - 4 CCD + 1 IOD (32 Nhân Zen 5 / 64 Luồng / 128 MB Cache)

100-000001249-02 - 2 CCD + 1 IOD (16 Nhân Zen 5 / 32 Luồng / 64 MB Cache)

Bây giờ vì không được đề cập rõ liệu các sản phẩm này có phải là Zen 5 hay Zen 5C SKUs không, các bể cache có dung lượng từ 256 MB đến 384 MB. Đối với SKU 96 nhân, nếu nó dựa trên kiến trúc Zen 5, thì nó nên mang trong mình một bộ nhớ cache L3 ấn tượng là 512 MB nhưng nếu nó dựa trên kiến trúc Zen 5C, thì nó nên giữ lại 256 MB cache.

+ EPYC Zen 5C: Lên đến 192 nhân, 384 MB Bộ nhớ Cache L3 (+50% so với Zen 4C về số lượng nhân/Bộ nhớ Cache L3)

+ EPYC Zen 5: Lên đến 128 nhân, 512 MB Bộ nhớ Cache L3 (+33% so với Zen 4 về số lượng nhân/Bộ nhớ Cache L3)

Phần còn lại của bộ sản phẩm khá là chuẩn với các phiên bản 8, 16, 24, 32, 36, 48, 64 nhân với các lựa chọn tiêu chuẩn và tối ưu hóa tần số. Tốc độ đồng hồ dao động từ thấp nhất là 2.0 GHz đến cao nhất là 4 GHz (tần số cơ bản), trong khi TDP dao động từ 155W/200W/210W/280W &300W+. CPU EPYC Turin của AMD sẽ hỗ trợ bộ nhớ DDR5-6000 MT/s lên đến 4 TB trên các bo mạch chủ có 8 DIMM, cung cấp lên đến 128 làn PCIe Gen5.

Dòng sản phẩm máy chủ AMD EPYC Turin "Thế hệ 5" dự kiến sẽ ra mắt vào cuối năm nay sau khi Zen 5 & Zen 5C chính thức được ra mắt cho các nền tảng máy tính để bàn và máy tính cá nhân như Granite Ridge và Strix Point. Dòng EPYC Turin Thế hệ 5 sẽ cạnh tranh với các CPU Intel Xeon Granite Rapids P-Core và Sierra Forest E-Core (288 Core). AMD gần đây đã xác nhận rằng hiện đang gửi mẫu CPU EPYC Turin Thế hệ 5 của mình.

Họ CPU AMD EPYC:| FAMILY NAME | AMD EPYC VENICE | AMD EPYC TURIN-DENSE | AMD EPYC TURIN-X | AMD EPYC TURIN | AMD EPYC SIENA | AMD EPYC BERGAMO | AMD EPYC GENOA-X | AMD EPYC GENOA | AMD EPYC MILAN-X | AMD EPYC MILAN | AMD EPYC ROME | AMD EPYC NAPLES |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Family Branding | EPYC 11K? | EPYC 9005 | EPYC 9005 | EPYC 9005 | EPYC 8004 | EPYC 9004 | EPYC 9004 | EPYC 9004 | EPYC 7004 | EPYC 7003 | EPYC 7002 | EPYC 7001 |

| Family Launch | 2025+ | 2025? | 2025? | 2024 | 2023 | 2023 | 2023 | 2022 | 2022 | 2021 | 2019 | 2017 |

| CPU Architecture | Zen 6? | Zen 5C | Zen 5 | Zen 5 | Zen 4 | Zen 4C | Zen 4 V-Cache | Zen 4 | Zen 3 | Zen 3 | Zen 2 | Zen 1 |

| Process Node | TBD | 3nm TSMC? | 4nm TSMC | 4nm TSMC | 5nm TSMC | 4nm TSMC | 5nm TSMC | 5nm TSMC | 7nm TSMC | 7nm TSMC | 7nm TSMC | 14nm GloFo |

| Platform Name | TBD | SP5 | SP5 | SP5 | SP6 | SP5 | SP5 | SP5 | SP3 | SP3 | SP3 | SP3 |

| Socket | TBD | LGA 6096 (SP5) | LGA 6096 (SP5) | LGA 6096 | LGA 4844 | LGA 6096 | LGA 6096 | LGA 6096 | LGA 4094 | LGA 4094 | LGA 4094 | LGA 4094 |

| Max Core Count | 384? | 192 | 128 | 128 | 64 | 128 | 96 | 96 | 64 | 64 | 64 | 32 |

| Max Thread Count | 768? | 384 | 256 | 256 | 128 | 256 | 192 | 192 | 128 | 128 | 128 | 64 |

| Max L3 Cache | TBD | 384 MB | 1536 MB | 384 MB | 256 MB | 256 MB | 1152 MB | 384 MB | 768 MB | 256 MB | 256 MB | 64 MB |

| Chiplet Design | TBD | 12 CCD's (1CCX per CCD) + 1 IOD | 16 CCD's (1CCX per CCD) + 1 IOD | 16 CCD's (1CCX per CCD) + 1 IOD | 8 CCD's (1CCX per CCD) + 1 IOD | 12 CCD's (1 CCX per CCD) + 1 IOD | 12 CCD's (1 CCX per CCD) + 1 IOD | 12 CCD's (1 CCX per CCD) + 1 IOD | 8 CCD's (1 CCX per CCD) + 1 IOD | 8 CCD's (1 CCX per CCD) + 1 IOD | 8 CCD's (2 CCX's per CCD) + 1 IOD | 4 CCD's (2 CCX's per CCD) |

| Memory Support | TBD | DDR5-6000? | DDR5-6000? | DDR5-6000? | DDR5-5200 | DDR5-5600 | DDR5-4800 | DDR5-4800 | DDR4-3200 | DDR4-3200 | DDR4-3200 | DDR4-2666 |

| Memory Channels | TBD | 12 Channel (SP5) | 12 Channel (SP5) | 12 Channel | 6-Channel | 12 Channel | 12 Channel | 12 Channel | 8 Channel | 8 Channel | 8 Channel | 8 Channel |

| PCIe Gen Support | TBD | TBD | TBD | TBD | 96 Gen 5 | 128 Gen 5 | 128 Gen 5 | 128 Gen 5 | 128 Gen 4 | 128 Gen 4 | 128 Gen 4 | 64 Gen 3 |

|

TDP (Max) |

TBD | 500W (cTDP 600W) | 500W (cTDP 600W) | 500W (cTDP 600W) | 70-225W | 320W (cTDP 400W) | 400W | 400W | 280W | 280W |

Nguồn: wccftech.com

Tin công nghệ

Tin công nghệ

Game

Game

Đánh giá

Đánh giá

Thủ thuật

Thủ thuật

Tư vấn

Tư vấn

Khám phá

Khám phá

Tin khuyến mãi

Tin khuyến mãi

Review - Video

Review - Video

PC DIY

PC DIY

Bình luận bài viết